実装図

はじめに

- File>design rules>Layers>coreで基板の厚みを変えられる。DRCを保存しておくと保持される。保存しないと保持されない。

- DRCを読み込んで保存しておくと、基板厚さ等も保持される。

- 使ったdrcファイルやCAMファイルも一緒にリポジトリに入れる

パターン

-

- 配線の電流容量

- 配線の電流容量(1mm / 1A、via0.5φ x 3個 / 1A)

シルク

- NAMEやVALUEがボード図で出てこないとき、自作パーツに>NAME、>VALUEを描いていないことが考えられる

- たまにライブラリを外部から落としてくると、>Namesになってたりするがこれでは反映されない。>NAME、>VALUEに変更

- シンボル上でNamesレイヤーに>NAME、Valuesに>VALUE、フットプリント上で、tNamesに>NAME、DocumentやtValueに>VALUEを書かないとでない

- それでもボード図上に出てこない時は、ボード図上でそのパーツをReposition Attributesすると直る。一度でもSmashしていじると、Repositionし続けるまでバグり続ける

- 同様に、tPlaceレイヤーにパーツの外形線が描かれてない場合は、登場しないので、注意

- tPlaceレイヤーには画像入れられたりもする

- 更新後、ライブラリをバージョンアップしてもボード図に反映されないことがある。その場合は一度ボード図を破棄するとうまくいくことがある

- ボード図に出てきても、ガーバーデータに出てきてない場合は、tValues等見せないレイヤーに来ている可能性がある

- LED等を載せるため反射率を稼ぐ等、基板を白くしたいときがある

- レジスト白の基板はレジストが剥がれやすいので、レジストは緑のままとして、シルクベタで反射を稼ぐ

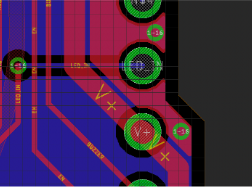

- 例えば黒丸の部分がLEDで、真ん中のボタン(SW1)部分を綺麗に光らせたいとするとこんな感じ

- ↑上の図では、実は、コンデンサもLEDも1種類しかなかったため、特に書いてないが、シルクで埋まるところは引き出し線で部材名を指定するとよい

- こういうイメージ。ビアの上のシルクは消えるからこれでは綺麗にならないが。

- シルクに画像を入れたいときは、run import-bmp.ulp

- 黒い面が白く、白い面が黒くなる(多分)ので、色味の反転をしてから読み込む

- 反転が大変なので、ボトムレイヤーに印刷するときは、先に画像を反転してからインポートするのが楽

- 2色だと、面積多いほうが多分白く塗られるので、選択は1色

- 正解の状態

- 失敗の状態

- スケールの数値を1からいじれば、大きさの変更も可能

- 読み込んだ画像レイヤーを、camファイルでtopシルクレイヤーかbottomシルクレイヤーに指定すれば、反映される

書き方

基本

- 手動で配線する

- 配線パズルが解けない場合は、ビア打って逃げる

- Edit→NET CLASSで電源ライン、GNDとかは設定しておく

- 配線の太さは手動で決める

- POWERは1.0〜1.5mmくらい

- 信号線は0.3〜0.5mmくらい

- 信号線は鋭角を避ける。エッチング時に失敗するため

- パスコンはまっすぐ通す

- 配線の電流容量(1mm / 1A、via0.5φ x 3個 / 1A)

- PADを出す場合は回路図側から配置すること

- 調べるとポリゴンツールを使う方法も出てくるが、回路図的にはつながってない子ができ、シルクの位置も自力で打つ必要があるため、絶対やめろ

- ピンヘッダはわざわざ長穴にしなくていいので、ライブラリ使う場合は直す→ライブラリ絶対使うな。ピッチが合わない。他のピンヘッダ使ってる基板から流用せよ。

- 回路は左から右に、電圧の高いものが上から下に書く(回路の素101からだったかも)

- TOPとBOTTOMをそれぞれ表示してチェック

- TOPからBOTTOMなど、線をレイヤーでまたぐときは、マウスの真ん中のボタンで入れ替えられる

レイヤー

- infoの上のLayer Settingsで見たいレイヤーを切り替えられる

- OK押さないと反映されないので注意

- TOP/BOTTOM

- ここで配線

- tPlace / bPlace

- 実際の基板のシルクに反映させたい情報なんでも。画像?も行ける。

- tOrigins / bOrigins

- パーツの原点がここで見える。これが表示されてないと原点行方不明になる

- tNames / bNames

- パーツのNamesが出る。これは実際の基板のシルクに反映される

- tValues / bValues

- パーツのValuesが出る。これは実際の基板のシルクに反映される…のか?

- 長いし、BOM見たらいいから、いらないものは消すのではなくtDocu/bDocuへ。

- 実際の基板のシルクに反映させたかったら、tPlace / bPlaceに移動。抵抗値等で使う。

- tCream / bCream

- はんだ塗ってショートさせておきたいところはこのレイヤーで書き込む

- tStop / bStop

- レジスト塗り禁止範囲。レジストとは、基板の表面に塗られている緑色のインク。

- シルクが被っていると印刷されないので注意。

- tKeepout /bKeepout

- 部品配置禁止範囲

- tRestrict / bRestrict

- 配線禁止範囲

- Drill

- スルーホール用穴

- Hole

- バカ穴

- Milling

- 文字通りエンドミル。

- Measures

- 寸法。寸法入力はMeasuresへ。寸法の真ん中ダブルクリックで触れる。

- 基板外形をMeasuresに書いておくとよい。

- tDocu / bDocu

- 実際のシルクに反映されない情報。

GND

- GNDはベタにするので割と適当でいい。

- ポリゴンツールでベタ作りたい部分を(基本は外形に沿う)描き、囲い切ったときにnameでGNDを指定。

- その後、ratsnestでベタGNDが打たれる。ratsnestってネズミの巣か?

- 見え方が変わるだけで実は何も起きない。つまりctrl+zでは戻れない。

- 基板が見づらくなるので、リセットしたい場合は、外形線を一度ゴミ箱に入れて、ctrl+Zで元に戻す

- ratsnestすればベタGNDは更新されるので、基板をいじりながらratsnestしていくのもあり。

- TOPとBOTTOMのベタGNDになるべく電位差が発生しないようにビアを打つ

- ビアを一つ打ち、nameをGNDにして、めっちゃコピーして打っていく

- パスコン等順序が大事な部分はポリゴンの中にポリゴンを書いて中を抜けばよい

- 基板の外周、ベタの周囲、とがっているところにviaをうってアンテナ化を防ぐ

- 配線で分断されているところを別のレイヤー経由で橋渡しする

- ベタGNDのISOLATEは0.3くらいにする 広めにしないとエッチング不足を引き起こす

- 使われてないGNDをむやみに延長しない(アンテナになって悪さする)

- GNDを強くする

- topのGNDベタができるだけ分断されないよう、配線を寄せる

- ビアの上にはシルクが印刷されないので注意

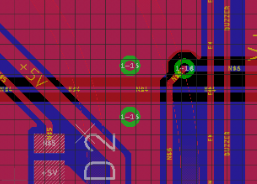

- レイヤーをViasにすれば、Viasがよく見える形で出てくる

配置

- 動かしてはいけない部品はLockしておく(nameも+ockされるので注意。)

- Lockされてたら+がxになる

- mirrorで部品の位置をTop/Bottomに反転。配線などは反転できない。

- パスコンはICの近くに、パスコンを通してICに電源供給

- ユニバーサル基板のスルーホール穴の間隔が0.1インチ (2.54mm)=100mil

- モーターの大電流の経路とマイクアンプ回路のような増幅回路をオーバーラップさせない

- 部品外形をシルクで描いて干渉を防ぐ

- ネジ頭と部品の干渉、銅箔の導通に注意

- ものによっては、配線不可領域がある

- change size 1.0などで文字サイズを修正

- Altキー押しながらならgrid無視で配置できる

コマンド

- 横のアイコンをクリックする方法と、検索バーっぽいところにコマンドを打ち込むことで、コマンドを指定できる

- 上ボタンで過去のコマンドに戻れる

- ripup で配線カット

- delete でそれ以外の削除(名前、部品、など)

- move でパーツの移動

- 複数を移動したい場合は、Groupで選択してから適当なところで右クリックすると、move Groupが選択できる

- パーツの中心がない場合は、tOrigin系を可視化すると出てくる

- 関連するものを一気に消したい場合は、Shift押しながらDelete

- ratsnest で配線最適化(unRoutedな配線が一番短い線で結ばれる状態)&ベタGND配置

- ベタGND配置時、infoでisolateを0.3に設定しないとただの真っ赤になる

- 見え方を変えるだけなので、ctrl+Zとかは使えない。注意。ベタGNDのISOLATEは0.3くらいにする

- ベタGNDで真っ赤真っ青になっちゃったら、ベタGND指定に使ったフレームを一度消して、ctrl+Zで視界復活

- TopとBottomで配線が被っている場合は配線をクリックして右クリックで切り替えられる

- change 〇〇 数字 でいろいろ変えられる

- size / width / drill

- polygon 多角形を書く。polygonの中にpolygonを入れると中を抜くことができる

- via 層同士をつなぐ。この上にシルクは印刷されない。

固定

- 配線固定用の穴はあけておくとよい

- φ3.2にするとこの結束バンドが入る

自動配線

- Net classを設定(POWER 1mm、そのほか0.5mmくらい)

- Autoroute

- 配線全消しはripup →GOボタン

捨て基板

- CAMするときに外形やmillingと同じようなレイヤーで指定すればどの寸法系レイヤーでも割と大丈夫?

- Dimensionレイヤーだと、外形線とかぶって、EAGLE上では見づらいけど、指定し忘れがない

- Vscoreレイヤーだと、外形線とは別のレイヤーになるので、見やすいけど、指定し忘れることがある

手順

- 捨て基板外形を描く。Vカットする場合は、最低基板サイズがあるので注意。

- 捨て基板外形の端から5mmずつのところに、4mmのドリル穴を開ける。Vカット時の固定用。

- 基板外形の一番外側の辺にVカットラインを引く。

- widthは0.5。カットの分だけ、外形側にオフセットすること。

- Dimensionと被ってもOK。Dimensionの線を消すとベタGNDが外形より外側に出て、銅箔部分を切断することになりかねないため。

- 穴加工する部分を作る。

- 上記手順のままでもくり抜きはされるが、微妙にRが残ってしまう

- millingでスロットを作る方法と、Dimensionでくり抜く方法がある

- millingでスロットを作る

- くり抜くと、基板の端材が飛ぶこともある(基板製造側で良しなにやってくれる可能性もあるが)ので、こちらがいいかも。外形寸法がずれる可能性はあるが。

- millingレイヤーで幅1の線で描き、MiterコマンドでRをつけると綺麗に描ける

- Dimensionでくり抜く方法

- 捨て基板部分に余分にエンドミルの逃がし部分を作る方法。外形幅+2mmくらい。

- 直線部分については、外形線を延長し、切り出し部分を描く

- 基板上にRをつける部分については、刃物が通り過ぎ切ってくれるように描く

- DimensionレイヤーでVカットラインも切り出しもやる時の注意

- 囲んでも抜かれないことがある

- このときは、Vカットラインを、一度別のレイヤー等(VScoreとか)に逃がして、Dimensionレイヤーで囲んでみるとよい

- 基板となる部分の見え方?が変になることがある。基板部分がグレーで抜く部分が黒く表示されるなど。製造上は問題ない。

- CAMで確認する

- Legacyからダブルクリックで外形やmillingレイヤーをエントリーしたあと、Vカットラインやmillingが出てなければ、レイヤーをダブルクリックで追加

面付け

- width0.5でLINEを引いてVscoreレイヤーに貼り付けることでできる

DRC(デザインルールチェック)

- 各基板製造メーカーが発行しているDRCファイルを、Tools>DRC>Loadで読みこみ、Checkで検査

- Selectすると、DRCに従って配線とか置き換わって死なので、やってしまったらCtrl+Zで戻る。

- ここがエラーなしになってないと、製造時にトラブりやすい。

ガーバーデータ出力

- DRCと違って、EAGLEで読み込むのではなく、CAMファイルを直接ダブルクリックして起動。

- 全てのレイヤーをレガシーから出すと、CAMが発行できる。

- Export zipで、zipファイル出力してくれる。便利。

エラー

- This job contains a mix of legacy and new cam outputs which may result in layer misalignment. このジョブにはレガシーと新しいカム出力が混在しているため、レイヤーの位置ずれが発生する可能性があります。

- 全項目を出力してないときに出るエラー。legacyになにか残らないようにしよう

ULP

- 部品番号を振りなおす

- ボード図で振りなおす場合,cmd-renumber.ulp

- 未配線をズームする

- run zoom-unrouted.ulp

- http://www.cadsoftusa.com/download-eagle/?language=en よりUser Language Programs (ULPs)を選択して,search for ULPにキーワードを入力しダウンロード。保存先はEAGLE インストールファイルのulpフォルダ

設計フロー

- 平面図や三面図上で大まかな配置を検討

- ratsnestをもとにパーツ配置(電源を考慮、unroutedが短くなることを考慮)

- 高さチェック(高さがシビアなら)

- 配置調整

- route, polygon

- DRC DRCパラメータは製造場所に合わせておく。例)#attach(bocco.dru:1073919281)

- net整合性確認

- 恐らく以下3つのANDでOKのはず。

- schとbrdそれぞれからnetlistを生成し、差異がないことを確認 File → export → netlist。これでどの足にもついていない浮きパターンによる短絡以外は確認できる。

- Unroutedが無いことを確認(後述)。schにあり、brdにない、引き忘れがないことを確認できる。

- DRCでoverlapがないことを確認。浮きパターンによる短絡を検知できる。

- シルク記入

- まずsmashとmoveで部品ごとにtNames, bNames層の部品名の位置を調節。レジスト開口とかぶらないように。

- レジスト開口とのクリアランスチェック:tStop, bStopを表示した状態でDRC。

- 危ないところがないか目視確認。銅箔は一層ずつONにして個々に+銅箔全層をONにして+unroutedが無いことを確認。

- unroutedはlength.ulpやstatistic-brd.ulpで確認可能。

- (気になるなら念のため)全パーツ寸法が間違っていないか確認

- 画像認識マークをつける(必要なら)

- 面付け、ミシン目作成(必要なら)

- . brdファイルのみ別名でコピーを作成し、開く。schがないという警告が出る。

- コピーしたい層すべてを表示

- group all; cut (> 0 0) でクリップボードにコピー、pasteで貼り付け

- Vカットを入れるには:Dimension層に0.2mm幅の線を端から端まで入れると(P板やJETPCBは)Vカットとみなしてくれます

- 心配なら VScore層に描画後、gerberで.vscなどの拡張子で出力、READMEに.vscはv-scoreですと書けばまず大丈夫でしょう。

- ミシン目を入れるには:Milling層に2mm幅の線でルーターカットを書き込み、0.6などのドリルを連ねてミシン目を作成。

- Milling層は、gerberで.milなどの拡張子で出力、READMEに.milは直径2mmのミルのセンターラインですと書いてください。

- 寸法記入(Measuring層)→基板発注時に少なくとも外寸は必要なので。

- ガーバー出力

- 好きな.camファイルを使ってガーバーを出力 例)#attach(boccov2_01.cam:1073919280)

- gerbvなどのビューワで最終確認

- ドリルと銅箔の位置関係(スルーホール)が正しいか

- シルクがレジスト開口に被ってないか(かぶっている場合は製造業者に「シルクをレジスト開口でカット」を明示するほうが無難)

- パッド/ランドのレジスト開口と他の信号線が近接しすぎていないこと

- 必要なパッドにメタルマスク開口があること

- 不要な部分にメタルマスク開口がないこと

- READMEファイルにファイル名とファイルの内容を記述 例)#attach(README.txt:1073919279)

- 基板発注

- 実装屋さんにパターン図および実装資料を提出

- パーツリスト: bom.ulpを走らせて、valueでグループすると員数なども数えてくれます。csvファイルが“;”区切りなので、適宜“,”に置換してからexcelで編集するとgood。カラムを追加(実装の有無、支給の有無、必要数、支給数)。

- マウンタ情報: mountsmd.ulpを走らせると出力される。mnt, mnb

- シルク図: tPlaceとDimensionをONにしてprint pdf。bPlaceとDimensionをONにしてprint mirrorチェックしてpdf。

- メタルマスクガーバー: cam processing時にtCream, bCreamを出力するようにしとけばOK。

- 外形ガーバー: out

- シルクガーバー: plc, pls

小技

主にやたら入り組んだ部品のパターンを作るときの座標入力を手動ではなく一括でやると便利という話。

座標入力が (x y) というコマンドで行えるのと、パッドの寸法を w x h というコマンドで行えるのを利用して、

エクセルなどの上でパッドサイズと座標を一覧化し、concatenateで整形してコマンド欄に貼り付けるとコピペ一回でパッド作成が終わって便利

レビューのポイント

すべての部品が定格内で動く

絶対最大定格は壊れはじめる限界なので、これで設計してはいけません。 想定されるすべてのユースケース(たとえば電源なら、充電中、電池が満充電、電池が放電終止、など含め)で動作範囲を満足するように設計しましょう。

- ピンの入力電圧範囲

- ピンの出力電流範囲

- キャパシタの耐圧(2〜3倍みておく)

- 抵抗の電力

- インダクタの電流

など

レビューポイント

Cのパッケージサイズが小さすぎないか

Cは小さいと耐圧が下がります。かかる電圧の2倍以上の耐圧をとっておくべきとされています。

パッケージ、耐圧、容量、温度特性、入手性の全条件を満たす製品が存在することを必ず確認しましょう。

Rはのパッケージサイズが小さすぎないか

Rは小さいと許容電力が下がります。

特に以下は注意:

- LEDの電流制限抵抗

- 電源ラインに入れるシャント抵抗的なもの

レジスト開口とパターンのクリアランス

レジストと銅箔がずれると開口から他の信号が覗いてしまって、最悪短絡する。

0.2mm程度は開いているといい。

パスコンを通ってからICに供給する

ICで出たノイズはパスコンを関門にして外(他のデバイスと共有しているベタGNDや電源ライン)に出さないようにします。

DCDC回路の設計

周辺部品の選定と、レイアウトについて細かく指示があるので、必ず仕様書を守るように。

レイアウト例が載っている場合はそれに則っておくと無難。 周辺部品についても選定例が載っている場合はそれに則っておくと無難。

DCDCのキャパシタは温度特性を明記したほうがいい。X5Rなど。

高速信号

クリスタルは短く配線

USB1.1、SPIなど10MHz前後以上の信号は反射を気にする

USB2.0、RAM、などは等長配線やテーパーが必要で、eagleのキャパオーバー。

電源が弱い

GND内やVCC内で電位が異なる場所ができてしまうと、アナログノイズや通信不良などいろいろ問題がおきます。

配線が細いと抵抗値が大きくなって電流の増減がそのまま電位の上下に変換されるので、電源ノイズが大きくなります。

- 電源はなるべく短く太く供給する

- 両面ベタGNDに対してviaを打って電位差を防ぐ